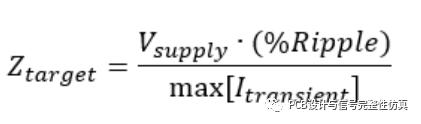

可能并没提供各个频段所需的PDN阻抗值,甚至翻完整个Datasheet都没有提及PDN,这样一个时间段就要使用到目标阻抗法来衡量仿真结果,毕竟有一个经验公式总比瞎搞好。

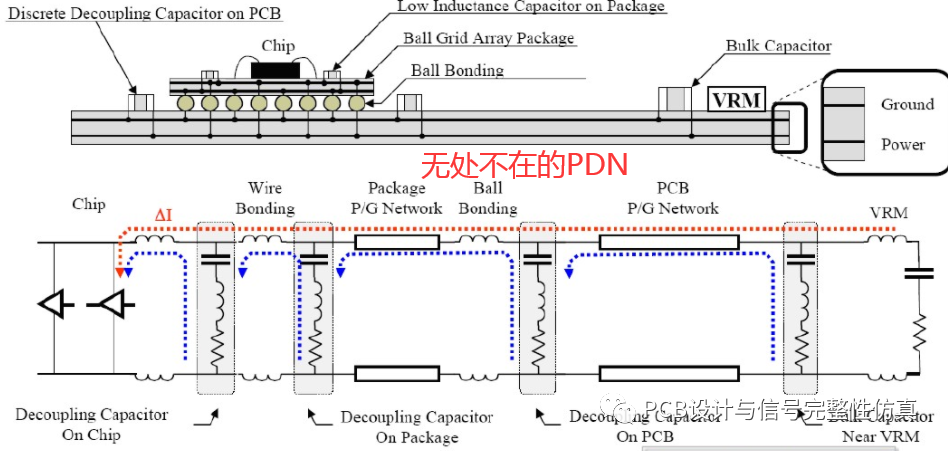

,全称是Power Distribution Network。为负载提供低噪声的电源,为信号提供低阻抗的返回路径等等都是它需要做的,它是衡量电源设计质量的重要指标。

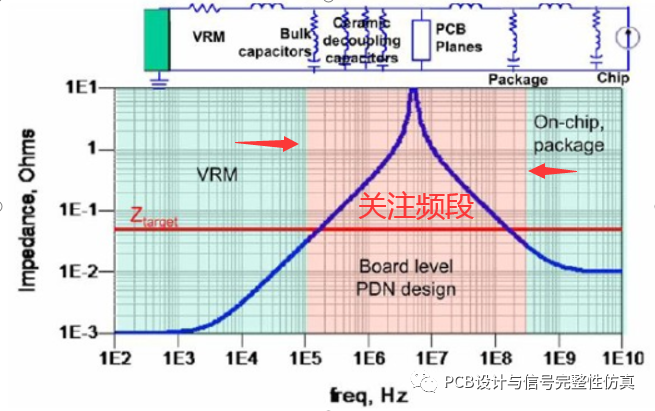

M,高频段的交给IC的片上电容,实际上对于PCB来说要关注的大概就在100K~100MHZ这样一个范围。

提供的DATASHEET中明确给出,而且是各个频段对应不同的目标值,通常低频要求目标值较低,随频率增高,这个值会逐渐增加(并不是说高频要求降低了,只是把这个任务的很大一部分交给了片上电容来完成)。

如果用最大电流来计算,会使得实际的目标阻抗值比较苛刻,正常情况下可以取0.5倍最大电流值计算即可,乐观点还可以0.3倍最大电流计算。

假设这个电源电压5V,纹波的峰峰值是3%,最大电流是2A,那么悲观的人得出的目标阻抗是:Ztarget=(5*0.03)/2=0.075;

不管心情如何,总归是算出了一个目标阻抗值,有这就能够适用于判断PDN阻抗是否达标。

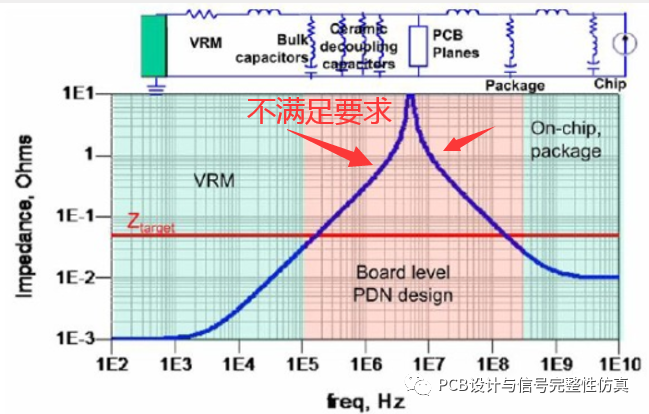

同样是这样图,我们假设Ztarget是我们计算出的目标阻抗,那么实际我们仿线MHZ这个范围内都是达不到要求的。

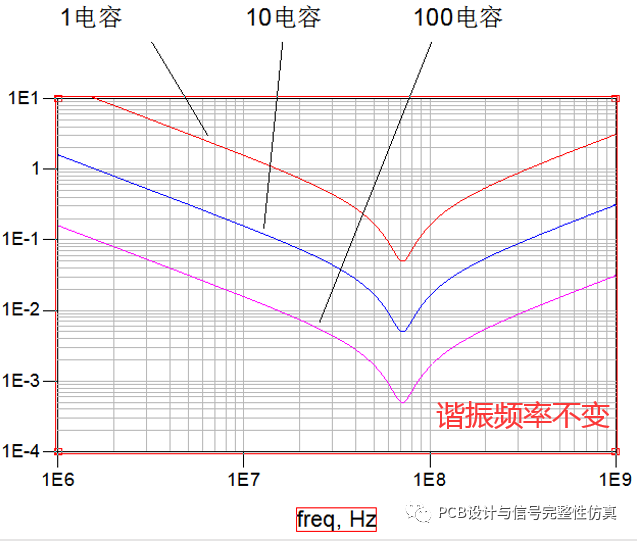

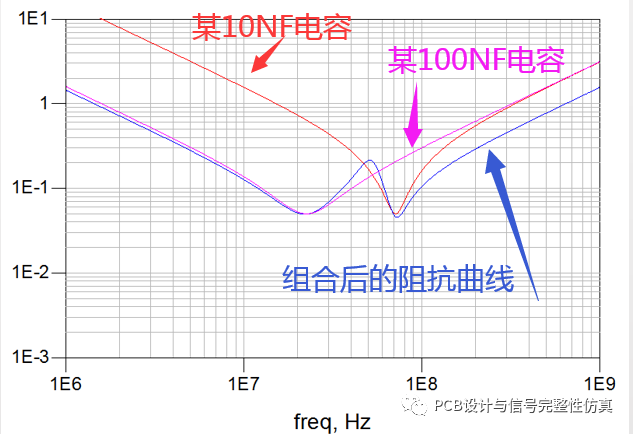

电容的应用从原理上来说分为两种,一种是并联大量的同类型电容,这样一个时间段可以大大降低电源阻抗,且并不会改变谐振频率。

在后仿真中,可以导入实际的PCB板和我们用到的电容库,让软件自动优化,给出限定条件下的最优解。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。举报投诉

)的基本设计规则告诉我们,最好的性能源自一致的、与频率无关的(或平坦)的

不同情况的设计,对于电容的安装和传播电感。图2表示的是各种设计情况对回路电感量的引入情况。图2 设计情况情况1-差的设计■设计人员不关注

1.首先参考芯片的参考设计,设计原理图,一般copy就可以;针对特殊情况,可以优化设计,优化去耦电容;2.设计叠成结构,GND与

层越近越好,建议参考demo;3.放置去耦电容;4.连接去耦电容;5.布线关键

。我们了解稳压器和芯片之间的连接有键合线,封装引线,过孔,平面,当芯片的电流有突变的时候,就会在这些连接上面产品压降,造成

分析概述 /

是由哪些部分所组成的? /

有何影响? /

【国产FPGA+OMAPL138开发板体验】(原创)4.FPGA的GPMC通信(ARM)EDMA

【先楫HPM5361EVK开发板试用体验】(原创)5.手把手实战AI机械臂