速率的不断的提高,特别是提升到 10Gbps 以上数量级后,电源完整性的测量成为关键测试项目之一,另外电平也慢慢变得小,使得它对电平的变化更加敏感。因而,近来不断地遇到客户咨询电源完整性的测试方案,所以的技术工程师们把电源完整性检测系统的技术背景和方案配置和关键性能指标整理如下。

PI(Power Integrity),即电源完整性,以前隶属于信号完整性分析专题,但是因为 PI 足够复杂和关键,现在已经把其单独拿出来作为一个专题去研究。快速而准确的仿真电源完整性至今仍然是一个有待突破的难题 (是德科技的ADS 高级仿真软件有专门支持电源完整性的方案)。

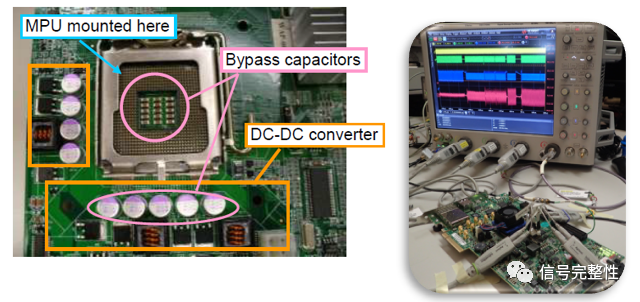

对于高速数字电路和系统,电源完整性(PI)的研究对象是电源分配网络PDN(Power Distribution Network)。以笔记本电脑为例,ACDC电源适配器供给计算机主板的是一个约 16V 的直流电源,主板上的电源分配网络要把这个 16V 直流电源变成各种电压的直流电源(如:±5V, +1.5V, +1.8V, +1.2V 等),给 CPU 供电,给各个芯片供电。CPU 和IC用电量很大,而且是动态耗电的,瞬时电流可能很大,大到几十甚至 100 多安培,也可能很小,小到低于 1mA,但无论电流如何变 化,电压必须平稳(即纹波和噪声必须较小),以保持 CPU 和 IC 的正常工作,这都对 PDN 提出了苛刻的要求。我们常见的电脑蓝屏现象,往往和电源完整性紧密关联,传统的方案有很多局限性,我们大家都希望随着 Keysight 的优异方案的普及,电脑蓝屏和其它电源完整性现象逐渐减少。

今天的电子电路(比如手机、服务器等领域)的切换速度、信号摆率比以前更高,同时芯片的封装和信号摆幅却越来越小,对噪声更加敏感。因此,今天的电路设计者们比以前会更关心电源噪声的影响。实时示波器是用来进行电源噪声测量的常用工具,但是如果使用方法和工具不对可能会带来完全错误的测量结果。

工程师选择示波器做电源噪声测量的一个原因是电源噪声带宽很宽,但是不能忽略的是,实时宽带数字示波器以及其探头都有其固有的噪声。如果要测量的噪声与“示波器和探头”的噪声在相同数量级,那么要进行精确测量将是十分艰难的一件事情。

所有的实时示波器都使用衰减器和放大器来调整垂直量程,在不同的量程设置下,其对应的放大比或衰减比是不同的,示波器的本底噪声也是不一样的。以 Infiniium S 系列示波器的 2.5GHz 型号DSOS254A 为例,在满带宽,2mV/div 设置下,其本底噪声是 120uVrms,在 10mV/div 设置下,其本底噪声就变为 172uVrms,表 1 是 S 系列示波器在不同量程设置下的本底噪声。从该表 1 我们大家可以得出一个结论,测量噪声时应尽可能使用示波器最灵敏,也就是最小,的量程档。但是示波器在最灵敏档下通常不具有足够的偏置范围可以把被测直流电压拉到示波器屏幕中心范围进行测试,表 2 是常见示波器支持的偏置范围,从表 2 我们能得出第二个结论,没有一台示波器支持的偏置范围可以覆盖常见的直流电源被测对象,因此通常需要利用 N7020A 这样的电源完整性专用探头将直流偏置范围提升到+/-24V,否则,你要么使用 AC耦合把直流电平滤掉只测量 AC 成分,要么使用隔直电容来完成测试, 但所有示波器仅在 1M 欧姆输入阻抗情况下支持 AC 耦合,在此条件下,示波器带宽会降到 500MHz,示波器自身的本底噪声会变大;使用隔直电容的缺点是将直流成分去掉的同时,也会把极低频信号滤 除,电源信号本身就是低频的,所以有机会把诸如电压缓慢跌落等现象掩盖了。表 1-1:Infiniium S 系列示波器在不同量程设置下的本底噪声,适用于电源完整性测试的设置最多只有 4 个,在图中以绿色标示。大部分情况下,应该使用每格 1mV~10mV 的设置。

表 1-1:对于电源纹波测试,建议使用最灵敏的垂直刻度,尽可能使用示波器的小量程,否则,示波器自身的本底噪声会带来较大的测量误差,该表给出 Infiniium S 系列示波器在不同量程设置下的本底噪声,因其内部采用线GSa/sADC,其指标远高于其它示波器。10 bits 的示波器,Infiniium S 系列示波器,其噪声相对小的多,而且硬件支持 2mV/div 的灵敏度,所以,放弃 8 比特,采用 10 bits 示波器,是最好的选择。

世面上也有一些其它 12 bits 的示波器,或者由于其内部 ADC 是商用

或者由于其 ADC 本身是 8bit(2G 带宽 6.25GSa/s 时只有 8bit)采用低带宽的 ADC 拼接技术因而本底噪声偏大,在和示波器自身硬件配合之后,其实际有效位比 Infiniium S 系列示波器要低 1 bit 左右,另外也不支持下一章介绍的电源完整性专用高阻探头。第二章 电源完整性时域分析之专用测试探头

基于同样的原因,在电源测量中也应该尽量使用 1:1 的探头而不是示波器标配的 10:1 的探头, 使用 10:1 的探头,示波器的最小量程会被放大十倍,示波器的噪声也会被放大。目前 N7020A 2GHz 1:1 单端有源探头,N2820A探头 500KHz~ 3MHz 带宽,衰减比为 1:330,最小可测信号电压为 3uV,电流为500nA,N2870A 1:1 35MHz 无源探头是最常被工程师认可的探头。其中 N7020A 是最适合电源完整性测试的探头,可测量毫伏以及亚毫伏级的信号,N2870A 是最便宜的探头,可测量 10mV 或以上的信号,N2820A 是最精密的探头,即可用作差分探头,也可用作电流探头,电压测量范围为 3 uV~1.2 V,电流测量范围为 500nA~5A,但带宽仅为 500 KHz~3 MHz 。

探头带来的噪声是在衰减器前面耦合进来的,在某些不正确的使用方法下,探头可能会带来额外的噪声,一个典型的例子就是使用长地线。为了方便测试,示波器的的无源探头通常会使用 15cm 左右的鳄鱼夹形式的长地线,这对于电源纹波的测试是不适用的,特别是板上存在

的场合。由于开关电源的切换会在空间产生大量的电磁辐射,而示波器探头的长地线又恰恰相当于一个天线,所以会从空间把大的电磁干扰引入测量电路。一个简单的验证方法就是把地线和探头前端接在一起,靠近被测电路(不直接接触)就可能在示波器上看到比较大的开关噪声。因此测量过程中应该使用尽可能短的地线。现在很多被测件要求测量出峰峰值为几毫伏的纹波和噪声,比如有些 10Gbps 以上的 SerDes 要求 3mv 峰峰值的电源纹波和噪声。这时候最好用 N7020A 来进行测量,它的直流阻抗为 50K 欧姆,对于毫欧甚至更高阻抗级别的被测电源来说,负载影响很小,测试精度非常高。

最后要注意的一点是,通常电源测试都规定了某个频率范围内的纹波和噪声,比如 20MHz 以内的,但为了分析电源噪声来源,需要在更宽的频率范围内分析,一般示波器的带宽在满足分析要求的同时,还要支持灵活的带宽限制功能,这对于减小高频噪声会有比较好的效果。

尽量使用示波器最小量程(硬件实现的量程,不是软件放大),以降低示波器本底噪声;

另外 N7020A 探头还支持选配 N7023A 点测套件,该套件提供了全系列的灵活的连接附件,除了传统的无源探头探头针尖和弹簧地针外还配有双列直插式探针,以及小夹子,可直接夹在最小达 0201 封装的贴片元件上。

要测量 PDN 性能,首先需要用示波器测试 CPU 和 IC 管脚的电源纹波和噪声。但是要精确衡量PDN 的性能,还需要测试PDN 的输出阻抗(随频率变化的阻抗)和PDN 的传输阻抗(也是随频率变化的阻抗),就像表征一个单

网络或双端口网络一样去表征 PDN。由于现在的 PDN 大都是开关电源结构,还需要测量PDN 或关键 DC 到 DC 转换器件的环路增益。小结一下,电源完整性的测量对象是电源分配网络 PDN。主要测量内容包括四部分:

电源完整性测试挑战和方法:毫欧级电源分配网络 PDN 的输出阻抗和传输阻抗测量

电源完整性分析对象主要是电源分配网络 PDN(Power Distribution Network)。要衡量 PDN 性能,只用示波器测试 CPU 和 IC 管脚的电源纹波和噪声是不够的,而且出现问题后也没有办法定位问题。要精确衡量 PDN 的性能,还需要测试 PDN 的输出阻抗(随频率变化的阻抗)和 PDN 的传输阻抗(也是随频率变化的阻抗),就像表征一个单端口网络或双端口网络一样去表征PDN。这就要用到网络分析仪工具。

1、PDN 的输出阻抗和传输阻抗是豪欧级的,想准确测试,是一件比较困难的事情。

2、PDN 工作时是带直流电压的,即带偏置的,需要网络分析仪有偏置测量的功能。

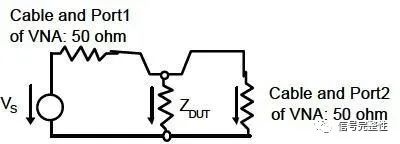

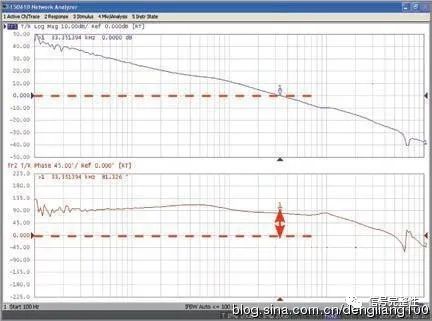

用网络分析仪测试毫欧级的输出阻抗,不能简单的用一端口测试方法,因为阻抗太小,反射太大。这时比较好的方法是用双端口测试方法,如图 3-1 所示。测试时用 S21 代替 S11。

假设探测试电缆电感约为 0,Z(DUT)远小于 Zo(VNA 端口阻抗),PDN 输出阻抗的计算公式如下:

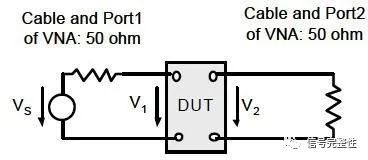

用网络分析仪测试毫欧级的输出阻抗,也是用双端口测试方法,如图 3-2 所示。

假设探测试电缆电感约为 0,Z11,Z21,Z22 远小于 Zo,PDN 传输阻抗的计算公式如下:

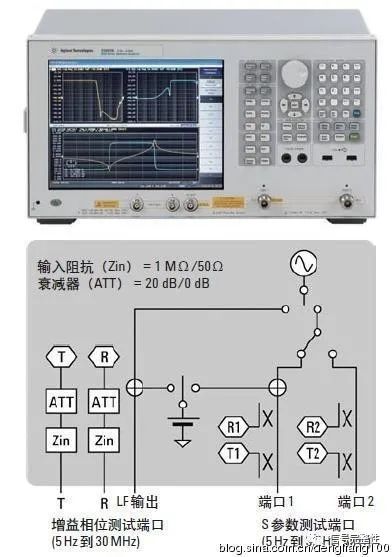

针对这种的特殊测量要求,是德科技的矢量网络分析仪 E5061B 推出了一个特殊的选件 3L5 帮助测试PDN。

网络分析仪的选件 3L5 可以在从 5 Hz 至 3 GHz 的率范围内提供常用的网络测量和分析功能。功能全面的低频网络测量能力 (包括内置的 1 MΩ 输入) 都被完美地集成到这个高性能的射频网络分析仪之中。E5061B-3L5 是研发环境中进行器件和电路测量的理想仪表和工具,选件 005 提供阻抗参数和等效电路分析。2、S 参数测试端口

E5061B-3L5 在其完全能够测量的从 5 Hz 到 3 GHz 的频率范围都有非常高的动态范围,这可以使您对各种几乎从直流到射频的器件来测试。

3、增益相位测试端口是德科技:双端口测量和 S参数 - 灵活应用网络分析仪3、增益相位测试端口

增益相位测试端口可以在从 5 Hz 到 30 MHz 的低频测量范围内直接把测试信号接入测量接收机。内置的 1 MΩ输入使您能够使用测量探头轻松地对所测电路内的放大器和直流 - 直流转换器的控制环路的参数做测量。接收机端口可以精确地测量放大器的 CMRR/PSRR 和 PDN 毫欧量级的输出阻抗,并且消除了测量中接地环路引入的测量误差。

E5061B-3L5 内置的直流偏置源可以从仪表内部把最高可达 ±40 Vdc 的直流偏置电压叠加到从端口 1 或 LF OUT 端口上输出的交流信号上。此外,如果在仪表的 S 参数测试端口上对被测器件做测量时,它还可以从 LF OUT 端口输出直流电压。

小结:E5061B-3L5 是专对于测试 PDN 而设计的网络分析仪,满足测量 PDN 输出阻抗和传输阻抗的测量要求。

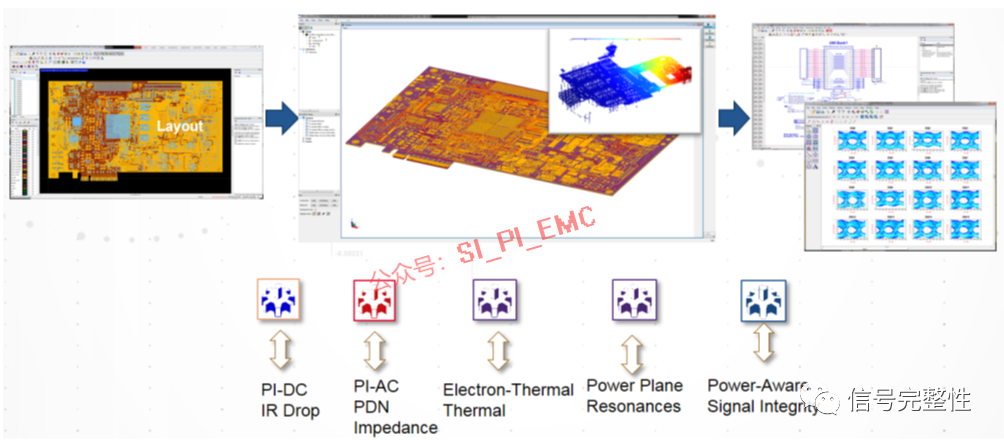

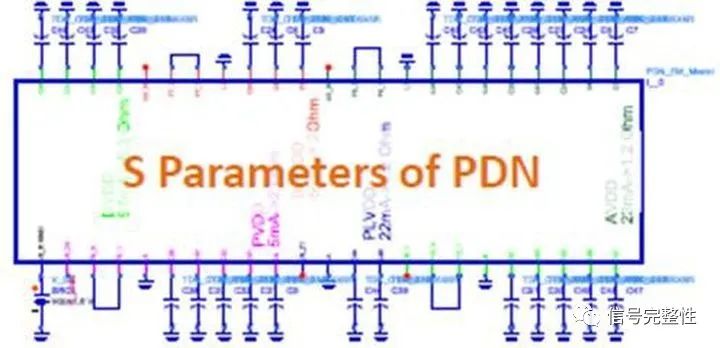

设计平台, 提供了完整的电源完整性设计解决方案。ADS 的版图设计环境集成了 SIPro/PIPro 仿真分析工具,通过对电源完整性进行仿真, 能够实现以下工作:直流电压降分析

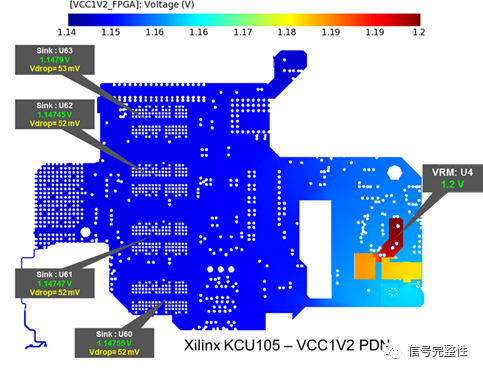

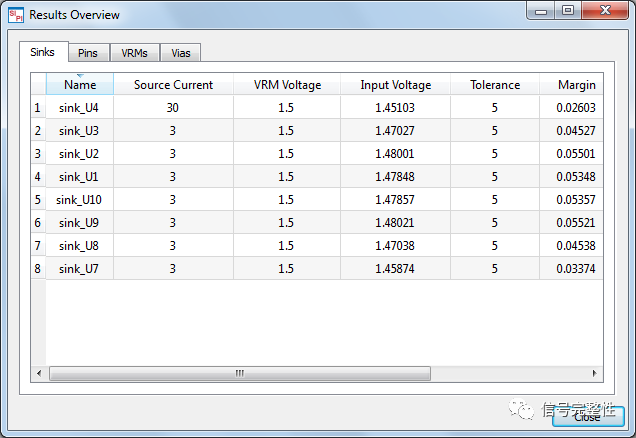

由于过大的直流电压降,落在IC 电源端的电压可能低于建议的最低电压。这可能会引起 IC 的故障。过高的电流密度在过孔处会生成过多的热量,引起电路板裂开或烧化,导致故障。PI-DC 可以计算直流条件下的电压、 电流,IR Drop (电压降)、 电源供应网功率损耗密度等。它能够在一定程度上帮助你识别IC 和

的管脚和连接过孔等在直流工作条件下流过的电流密度,显示芯片管脚电压, 并给出设计裕量。

PI-AC 分析用于提取PDN 阻抗特性,并能显示电流密度, 了解热点区域。提取的阻抗网络可以直接转化为 ADS 的原理图,与电压调节模块(VRM)模型和去耦电容进行优化。

其中,∆ 表示最大允许的电源纹波, 是最大瞬态电流波动,通常设置为芯片最大电流的一半。

ADS 提供了 10 余种优化方法, 能轻松实现去耦电容参数的快速搜索,实现最佳性能。通过一系列分析去耦电容通过电流的大小, 可以剔除冗余电容, 降低设计成本。

电源平面谐振分析可以计算配电网络(PDN)的自谐振频率和相应的 Q 值。它能够在一定程度上帮助你实现去耦电容和过孔的优化布置。电源平面谐振会干扰敏感的

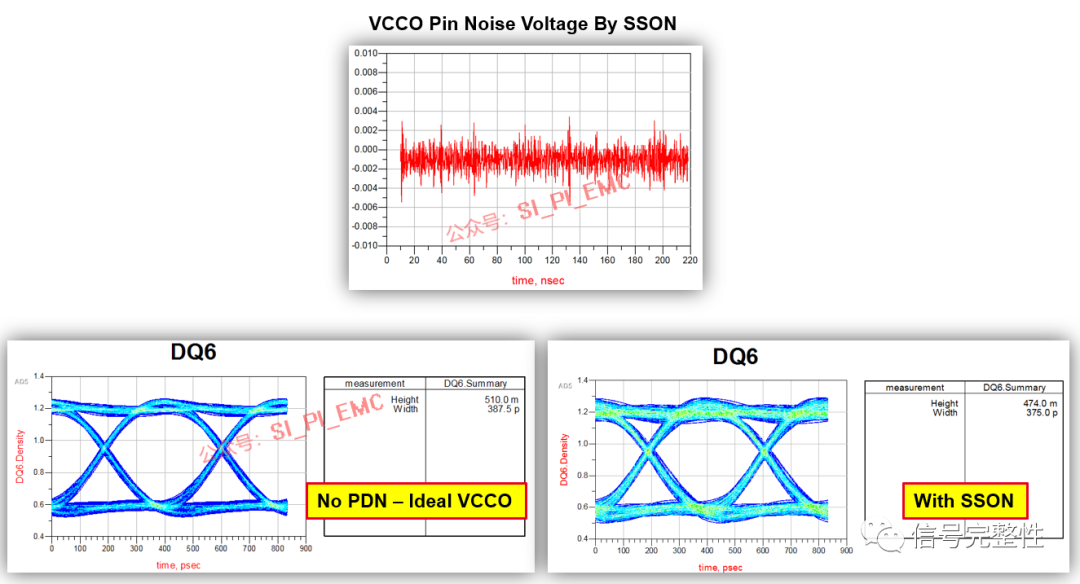

模型(通常是 SPICE 模型), 这类模型通常难以从芯片厂家直接获得,并且仿真时间很长。IBIS 模型是由 IBIS Forum 提出的一种行为级模型, 它通过 I-V 和V-T 曲线表征芯片输入输出 Buffer 特性, 不涉及元器件的内部电路设计, 可以有明显效果地保护厂家的知识产权, 因此, 芯片厂家更愿意提供 IBIS 模型给用户进行信号完整性的设计。IBIS 5.0 和 5.1 的标准中提出了多个新特性(BIRD95.6,98.3,141), 用于支持对芯片电源特性的描述。ADS 软件在业界率先实现了对以上新特性的支持,解决了之前的 IBIS 模型不能用于电源完整性分析的问题。

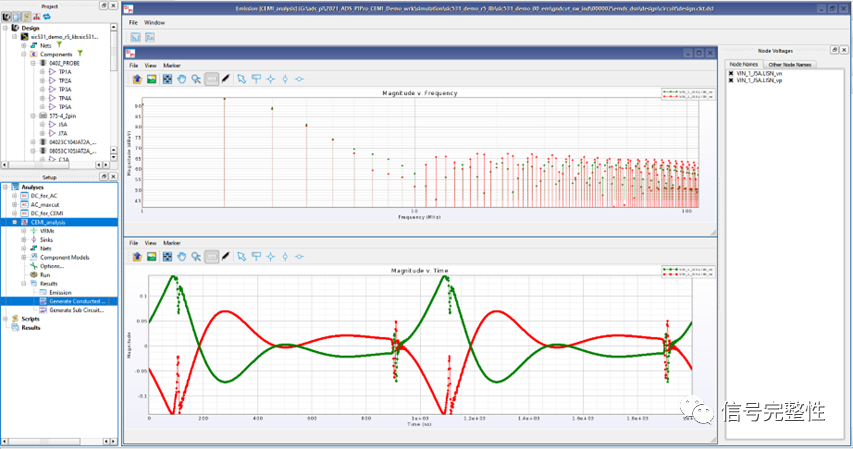

检测分析,传导就是EMC的一种。为了更好地发现、避免以及解决传导的问题。在PIPro中可通过CEMI对电路进行传导的仿真分析。下图所示为CE的仿真结果。

芯片通常安装在印刷电路板(PCB)上,由电源分布网络(PDN)供电。使用每个集成电路芯片时,都必须考虑到它对电源分布网络的影响。大多数集成电路芯片只在改变状态时消耗电流,这种不规律的用电给PDN带来了很大失真,产生电源完整性的问题。电源分布网络出问题,会对其它电路产生干扰,增加噪声,进而导致信噪比降 低,影响集成电路芯片输出端口处的信号完整性。在最坏的场景中,电源噪声有可能对集成电路的工作产生负面影响。同样,直流电源电平的波动也会干扰集成电路的正确工作。

限制噪声电平。可是所有补偿方法在最大限度减少直流电源失真的同时,也都存在各自的限制。

中的材料缺陷会产生等效的串联电阻。电容器和封装会产生等效的串联电感。这些寄生效应会极度影响电容器的技术特性。电容器在高频范围内的特性更像是电感或

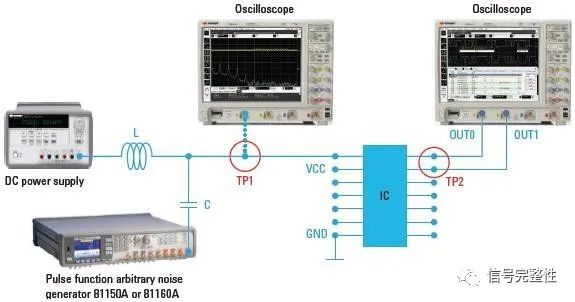

方案配置在真实条件下测试元器件和电路是一个必不可少的环节。在这样的一个过程中,工程师可以评估PCB 的设计和功耗。测试还可以使工程师进一步探索被测对象,增强被测件的总体性能。图 5-1 显示了在设计过程中模拟线 中汇总了该方案的组成部分。在图 5-1 所示的配置中,Keysight E36311A 直流电源用于模拟被测电路中的电压源。Keysight 81160A 任意波形噪声发生器用于模拟信号失真。电源和噪声发生器的输出通过电感和电容器所构成的网络合并。电感 L 可以有效的预防信号的射频分量进入直流电源。电容器 C 能够尽可能的防止信号发生器(81160A)直流负载效应。这个网络在

中经常被称为偏置 T 形接头,因为它的形状为 T 形,并能够给大家提供“直流偏置”。图 5-1. 模拟真实条件的测试装置

Keysight Infiniium S 或 9000 系列示波器的一个主要特性是它能够校准测试配置。换句话说,示波器能够确认向被测器件(DUT)的输入端,是否施加了正确的直流电压和失线)处的连接。)

(TP2)上,使用同一台 9000 系列示波器来分析集成电路芯片输出信号(图中画了两台示波器,但你可以只用一台示波器)。一旦 81160A 添加的失真变得太大而无法补偿时,集成电路芯片将产生物理层错误或协议层错误。这两类错误可以用示波器检测和分 析。

为了仿真线A 能够生成上升时间/下降时间仅为 1 ns 的快速脉冲、随机噪声和各种任意波形。该发生器的另一个关键特性是能够内部合并不一样的信号,因此能同时叠加电源分布网络中的高斯白噪声和间歇性毛刺。这种通道叠加(Channel Add)功能不仅仅可以灵活地生成复杂波形,而且避免了外部接线的麻烦。可选择的噪声发生器波峰因数, 以及可以在20 1 天内不重复噪声码型的功能,确保噪声接近于随机噪声,而不是确定性噪声(这些功能是其它同类仪器没办法提供的)。图 5-2 显示了通道叠加和噪声产生功能的示例。在此例中,81160A 在通道 1 生成高斯白噪声,在通道 2 生成高斯脉冲,然后在内部合并这两种信号,再与电源的直流信号叠加,得到黄色轨迹。这是在时域中测得的结果。图 5-2 所示的绿色轨迹是FFT频谱分析结果 。利用这个功能,工程师可以深入分析被测器件的输出性能。

工程师在开发新的电子器件时会遇到许多挑战。印刷电路板上的集成电路芯片密度日益提 高,因此评测直流电源性能以及电源分布网络(PDN)对设计中其他元器件的影响也慢慢的变重要。要正确评测设计,工程师需要用能够模拟真实条件的测试配置。当工程师分析自己的设计时,测试方案各组件能发挥及其重要的作用,帮他们最大限度减少失真并提高电源和信号的完整 性。

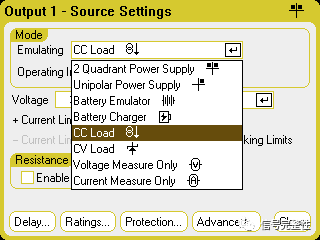

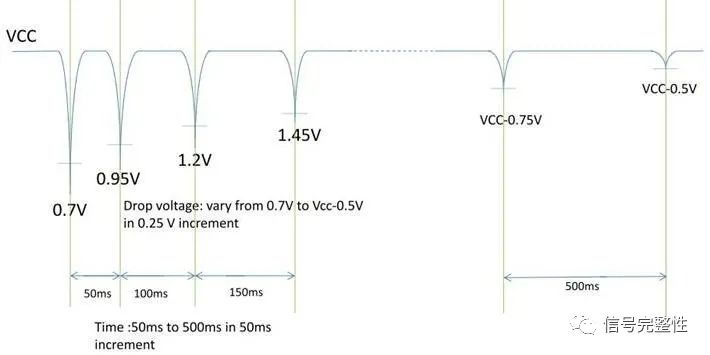

N676X 系列精密模组或 N678X 系列 SMU 模组,具有噪声小,精度高,电压调节速度快等特征,可用于任意瞬态供电电压模拟,用于测试电路或 IC 在电压瞬态时的可靠性。典型配置

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。举报投诉

互联的等效模型。驱动电路和接收电路采取了IBIS模型(也可以用SPICE模型来替代)。利用该

本帖最后由 EMChenry 于 2015-8-24 14:20 编辑 嵌入式电容材料的

? SI 只是针对高速信号的部分,这样的理解没问题。如果提高认知,将SI 以大类来看,SI&PI&EMI 三者的关系:所以,基础知识系列里还是

【国产FPGA+OMAPL138开发板体验】(原创)4.FPGA的GPMC通信(ARM)EDMA

【先楫HPM5361EVK开发板试用体验】(原创)5.手把手实战AI机械臂